本文摘自太平洋电脑网,原文链接:https://news.pconline.com.cn/1503/15032187.html,侵删。

近日,在比利时安特卫普举办的未来峰会上, IMEC(微电子研究中心) 发布报告,探讨了直至2036年左右的半导体工艺、技术路线图。

IMEC是一家成立于1984年的权威半导体研究机构,位于欧洲,研究方向包括微电子、纳米技术、信息通讯系统技术(ICT)、芯片制程技术、元件整合、纳米技术、微系统和元件、封装等各个方面。

IMEC的名气不如Intel、ARM、ASML、台积电、三星、中芯国际等等芯片设计、制造商,但同样是重量级玩家,尤其是在基础技术研究、行业标准化方面扮演着至关重要的角色,与上述巨头都有密切合作,还在与ASML合作推动EUV光刻技术。

在谈论路线图之前,首先解释一点,X纳米工艺行业都标注为“Nx”(nanometer),而在纳米之后将是“埃米”,标注为“Ax”。事实上,2nm之后就开始使用埃米了,A14就等于1.4nm。

IMEC预估的路线图上, 每一代工艺稳定间隔两年时间推进 ,但目前看应该是初步投产时间,而非量产商用时间,比如N3 3nm,路线图上标注2022年,但今年是看不到实际产品的。

之后将陆续是N2、A14、A10、A7、A5、A3、A2,最后的A2也就是0.2nm,预计在2036年左右实现。

当然,不同厂商的路线图是不一样的,比如Intel还有一个A18,台积电则跳过了N3。

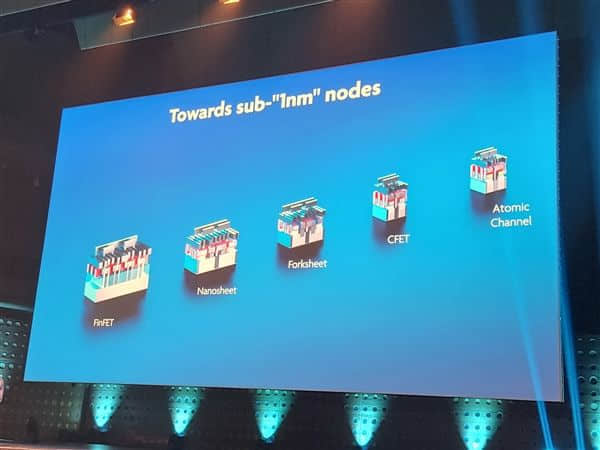

在晶体管技术层面,IMEC认为, 现有的FinFET只能维持到N3工艺,之后的N2、A14将转向GAA环绕栅极、Nanosheet纳米片技术,而再往后的A10、A7会改用Forksheet。

A5时代开始必须使用CFET互补场效应晶体管,而到了A2工艺,还要加入Atomic原子通道。

自然,每一家厂商的技术路线也不一样,哪个工艺节点上应用什么技术,也都有各自的考量。

值得一提的是,对于栅极间距(Meta Pitch)这一衡量工艺先进性的重要指标,未来进一步缩减将越发困难,A10工艺可以达到16nm,A7工艺只能到16-14nm,之后的A5、A3、A2工艺都停留在16-12nm。

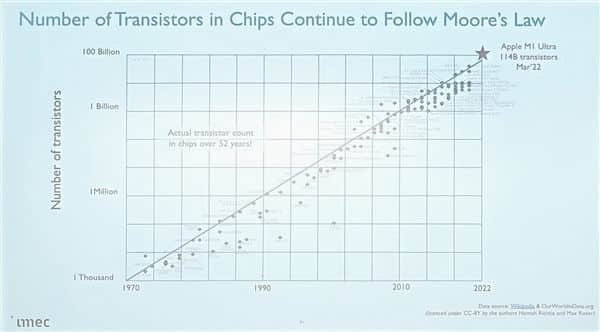

IMEC统计历史数据后发现,52年过去了,从晶体管数量角度看,摩尔定律依然坚挺,而目前的晶体管数量之王属于苹果M1 Ultra,通过双芯封装达到了1140亿个。

相关阅读 >>

苹果 apple pay later“先买后付”或推迟到 2023 年 ios 16.4 发布

奥特曼人间体谁吃得最多,东光太郎一次吃十碗,不愧是人间体吃货

更多相关阅读请进入《新闻资讯》频道 >>