本文摘自太平洋电脑网,原文链接:https://news.pconline.com.cn/1488/14883445.html,侵删。

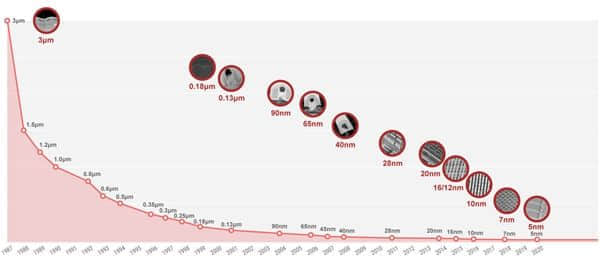

据techpowerup报道称,台积电正在开发3nm的工艺制程,包括了N3、N3B和N3E多个节点。

据了解,台积电原计划在2022下半年量产N3节点,N3E量产计划为2023年下半年。

但由于作为3nm简化版的N3E节点,量产率较高,台积电希望早日实现商业化,可能提前到2023年上半年。

N3E的工艺流程也已经提前准备好了,工艺流程在这个月底就会确定。

据悉, N3E在N3基础上减少了EUV光罩层数,从25层减少到21层,逻辑密度低了8%, 不过仍比5nm的N5制程节点要高出60% ,并且具有更好的性能、功耗和产量。

相比之下,据说N3的逻辑密度比N5高 70%。

还有N3B,据说是针对某些客户的 N3 的改进版本,不过我们目前对N3B节点知之甚少。

无论N3E还是N3B,都不是用于取代N3,只是让客户有更多的选择,在不同产品上有更好的性能和功耗表现。

相关阅读 >>

台积电 1nm 新厂最早有望于 2026 年动工,2028 年量产

苹果将是台积电 3nm 工艺量产后主要客户,首款产品为 m2 pro 芯片

业内人士:台积电已明显缩减材料拉货力道 预计2023年5月前都不会增强

豪掷400亿美元,台积电计划在中国台湾建造更多3nm芯片工厂

更多相关阅读请进入《台积电》频道 >>